| Board | Picture | Description |

|---|---|---|

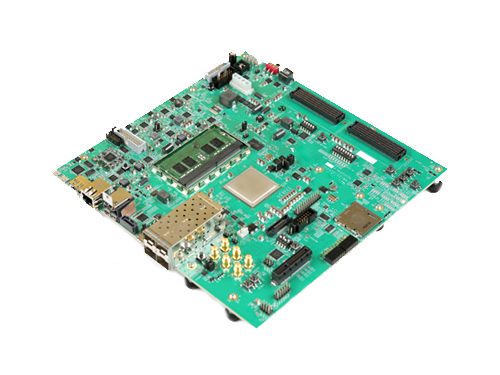

Xilinx Zynq UltraScale+ MPSoC ZCU102 Evaluation Kit (ZCU102) |

|

The ZCU102 Evaluation Kit enables designers to jumpstart designs for automotive, industrial, video, and communications applications. This kit features a Zynq® UltraScale+™ MPSoC with a quad-core Arm® Cortex®-A53, dual-core Cortex-R5F real-time processors, and a Mali™-400 MP2 graphics processing unit |

This repository provides Xilinx's firmware artifacts for the ZCU102 board meant to accelerate ROS 2 robotic applications.

NOTE: This repository is has various GB of data. Due to GitHub size restrictions, the whole source code is available under releases. Refer to each corresponding's release firmware/ARTIFACTS.md file for a description of all the artifacts included.

According to REP-2008's proposal.

| Capability | KRS alpha1 |

|---|---|

1. Kernel Levels |

|

1.i level I kernels |

✓ |

1.ii level II kernels |

|

1.iii level III kernels |

|

2. Build System |

|

2.i ament extensions |

✓ |

2.ii ament_acceleration support |

|

3. Build Tools |

|

3.i hardware emulation (hw_emu) |

✓ |

3.ii hardware emulation (sw_emu) |

✓ |

3.iii image tooling |

✓ |

3.iv Linux kernel |

✓ |

3.iv.a modern Linux kernel |

✓ |

3.iv.b LTS Linux kernel |

|

3.v hypervisor |

✓ |

3.v.a no control domain VMs |

✓ |

3.v.b guest VMs in disk |

✓ |

3.v.c control domain in disk |

✓ |

3.v.d no control domain VMs in disk |

|

3.vi network booting |

|

3.vi.a boot artifacts |

|

3.vi.b rootfs |

|

3.vi.c multi-network boot |

|

3.vi.d secure network booting |

|

3.vi.e save in disk network boot |

|

4. Benchmarking |

|

4.i kernel benchmarking |

✓ |

4.ii ROS 2 acceleration benchmarking |

|

5. Documentation |

|

5.i in-code documentation |

✓ |

6. Testing and CI |

|

6.i acceleration_examples |

✓ |

No quality is claimed according to REP-2004. This package should only be used in workstations to produced valid firmware for the targeted hardware.

Footnotes

-

Aligns with Vitis 2020.2 release. ↩